(For Maker Faire Taipei 2017 customers: English explanation is written after Japanese.)

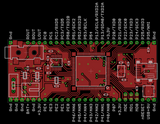

お待たせしました。MFT2015で頒布したPICUAL(PERIDOT用LCDシールド)のデモデータを公開しました。

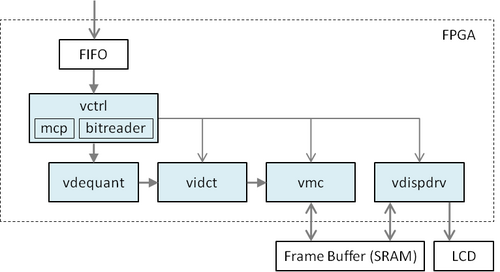

- PERIDOT用コンフィグレーション (cq_viola_top.rbf)

- プロジェクトファイル一式は以下にあります。

https://github.com/kimushu/peridot/tree/feature/picual/fpga/peridot_picual - コンパイル済みのバイナリで試したい方は、PERIDOT RBF-WRITERにて以下のRBFをPERIDOTに書き込んでください。

https://github.com/kimushu/peridot/raw/feature/picual/fpga/peridot_picual/output_files/cq_viola_top.rbf

- プロジェクトファイル一式は以下にあります。

- 動画再生制御プログラム (boot.elf @ lcdunit_ckplay)

- 上記コンフィグレーションでは、NiosIIのブートローダがSDカードからELFバイナリを起動するようになっています。

SDカードをFAT16or32でフォーマットし、"PERIDOT"というディレクトリを作って"boot.elf"という名前で動画再生プログラムを入れておきます。このプログラムは、同じくSDカードの"PERIDOT"ディレクトリから"*.ck"というファイルを検索して、順番に再生します。いまのところ、タッチセンサによる動画切り替え等の機能はありません。 - 本プログラム起動後の約15秒間は、タッチセンサのテスト機能が動きます。PICUAL製造後の動作テストに使っていました。

- 動画再生制御プログラムは上記プロジェクトファイルのsoftwareディレクトリ内にあります。

https://github.com/kimushu/peridot/tree/feature/picual/fpga/peridot_picual/software/lcdunit_ckplay - コンパイル済みのバイナリもあります。以下のファイルをお使い下さい。

https://github.com/kimushu/peridot/raw/feature/picual/fpga/peridot_picual/software/lcdunit_ckplay/boot.elf

- 上記コンフィグレーションでは、NiosIIのブートローダがSDカードからELFバイナリを起動するようになっています。

- 動画エンコーダ

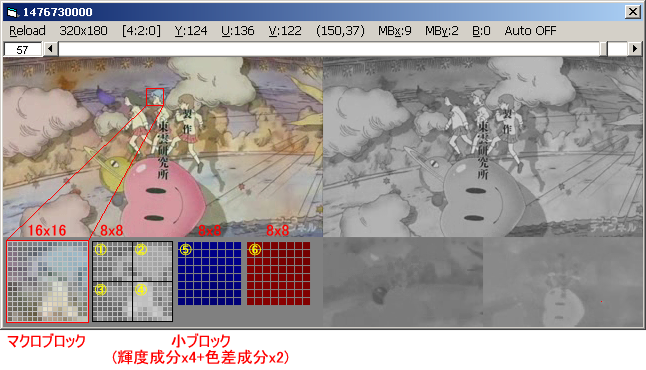

- 本サンプルでは、動画フォーマットとして長船氏によるCKコーデックが用いられています。

エンコーダ(に音声付加機能を追加したもの)の公開許可をいただきましたので、以下で公開します。

https://github.com/kimushu/ck_enc

- 本サンプルでは、動画フォーマットとして長船氏によるCKコーデックが用いられています。

- 動画データサンプル

- CC-BYな動画をckファイルに変換しておきましたので、置いておきます。(提供元:http://mazwai.com/)

raccooncomeandgo.ck

- CC-BYな動画をckファイルに変換しておきましたので、置いておきます。(提供元:http://mazwai.com/)

Demonstration and sample data for PICUAL & PERIDOT board:

- FPGA configuration for PERIDOT (cq_viola_top.rbf)

- Write this file (cq_viola_top.rbf) to PERIDOT using PERIDOT RBF-WRITER.

- If you want to edit FPGA configuration as you like, you can use the Quartus project file uploaded here: https://github.com/kimushu/peridot/tree/feature/picual/fpga/peridot_picual

- Video play control program (boot.elf @ lcdunit_ckplay)

- Prepare a SD-card and format with FAT16 or FAT32.

- Make "PERIDOT" directory at the root of SD-card

- Copy this file (boot.elf) into "PERIDOT" directory on SD-card.

- If you want to edit control program, you can customize Nios II EDT project files uploaded here: https://github.com/kimushu/peridot/tree/feature/picual/fpga/peridot_picual/software/lcdunit_ckplay

- This program includes touch panel tester and video player. After power-on, touch panel tester starts first, video player starts after about 15 seconds.

- Video encoder

- In this demonstration, @s_osafune's "CK-codec" is used for video compression.

- The encoder for CK-codec (ck_enc) is uploaded here: https://github.com/kimushu/ck_enc

- After video compression, copy encoded video files (*.ck) into "PERIDOT" directory of SD-card.

- Pre-encoded video sample

- raccooncomeandgo.ck (License: CC-BY. From http://mazwai.com/)

最近のコメント